# 192 kHz Digital Audio Interface Receiver

| Features                                                                                       | ♦ 32 kHz to 192 kHz Sample Frequency Range                                                  |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| <ul> <li>Complete EIAJ CP1201, IEC-60958, AES3,</li> <li>S/DDLE Compatible Reserver</li> </ul> | <ul> <li>Low-Jitter Clock Recovery</li> </ul>                                               |

| <ul> <li>S/PDIF-Compatible Receiver</li> <li>+3.3 V Analog Supply (VA)</li> </ul>              | <ul> <li>Pin and Microcontroller Read Access to<br/>Channel Status and User Data</li> </ul> |

| ♦ +3.3 V Digital Supply (VD)                                                                   | ♦ SPI <sup>™</sup> or I <sup>2</sup> C <sup>®</sup> Control Port Software Mode and          |

| ♦ +3.3 V or +5.0 V Digital Interface Supply (VL)                                               | Stand-Alone Hardware Mode                                                                   |

| <ul> <li>8:2 S/PDIF Input MUX</li> </ul>                                                       | <ul> <li>Differential Cable Receiver</li> </ul>                                             |

| <ul> <li>AES/SPDIF Input Pins Selectable in Hardware<br/>Mode</li> </ul>                       | <ul> <li>On-Chip Channel Status Data Buffer Memories</li> </ul>                             |

| <ul> <li>Three General Purpose Outputs (GPO) Allow<br/>Signal Routing</li> </ul>               | <ul> <li>Auto-Detection of Compressed Audio Input<br/>Streams</li> </ul>                    |

| <ul> <li>Selectable Signal Routing to GPO Pins</li> </ul>                                      | <ul> <li>Decodes CD Q Sub-Code</li> </ul>                                                   |

| <ul> <li>S/PDIF-to-TX Inputs Selectable in Hardware<br/>Mode</li> </ul>                        | OMCK System Clock Mode                                                                      |

| <ul> <li>Flexible 3-wire Serial Digital Output Port</li> </ul>                                 | See the General Description and Ordering Information on page 2.                             |

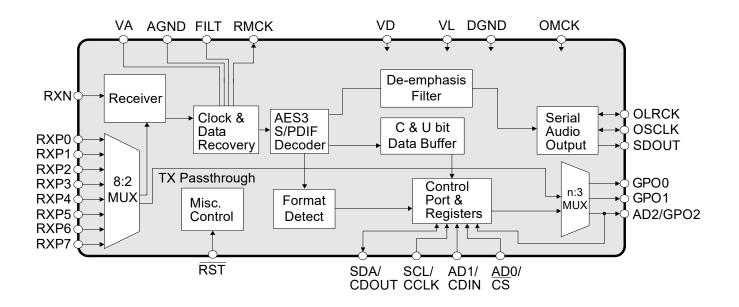

### **General Description**

The CS8416 is a monolithic CMOS device that receives and decodes one of eight stereo pairs of digital audio data according to the IEC60958, S/PDIF, EIAJ CP1201, or AES3 interface standards. The CS8416 has a serial digital audio output port and comprehensive control ability through a selectable control port in Software Mode or through selectable pins in Hardware Mode. Channel status data are assembled in buffers, making read access easy. GPO pins may be assigned to route a variety of signals to output pins.

A low-jitter clock recovery mechanism yields a very clean recovered clock from the incoming AES3 stream.

Stand-alone operation allows systems with no microcontroller to operate the CS8416 with dedicated output pins for channel status data.

The CS8416 is available in 28-pin TSSOP, SOIC, and QFN packages in Commercial grade (-10° to +70° C) and Automotive grade (-40° to +85° C). The CDB8416 Customer Demonstration board is also available for device evaluation and implementation suggestions. Please refer to "Ordering Information" on page 60 for complete ordering information.

Target applications include A/V receivers, CD-R, DVD receivers, multimedia speakers, digital mixing consoles, effects processors, set-top boxes, and computer and automotive audio systems.

### TABLE OF CONTENTS

| 4  | CHARACTERISTICS AND SPECIFICATIONS                                | c  |

|----|-------------------------------------------------------------------|----|

| Т. | SPECIFIED OPERATING CONDITIONS                                    |    |

|    | ABSOLUTE MAXIMUM RATINGS                                          |    |

|    |                                                                   | -  |

|    | DC ELECTRICAL CHARACTERISTICS                                     |    |

|    | DIGITAL INPUT CHARACTERISTICS                                     |    |

|    | DIGITAL INTERFACE SPECIFICATIONS                                  |    |

|    | SWITCHING CHARACTERISTICS                                         |    |

|    | SWITCHING CHARACTERISTICS - SERIAL AUDIO PORTS                    |    |

|    | SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MODE               |    |

| -  | SWITCHING CHARACTERISTICS - CONTROL PORT- I <sup>2</sup> C FORMAT |    |

| 2. | PIN DESCRIPTION - SOFTWARE MODE                                   |    |

|    | 2.1 TSSOP Pin Description                                         |    |

|    | 2.2 QFN Pin Description                                           |    |

| 3. | PIN DESCRIPTION - HARDWARE MODE                                   |    |

|    | 3.1 TSSOP Pin Description                                         |    |

|    | 3.2 QFN Pin Description                                           |    |

|    | TYPICAL CONNECTION DIAGRAMS                                       | -  |

| 5. | APPLICATIONS                                                      |    |

|    | 5.1 Reset, Power-Down and Start-Up                                |    |

|    | 5.2 ID Code and Revision Code                                     |    |

|    | 5.3 Power Supply, Grounding, and PCB Layout                       |    |

| 6. | GENERAL DESCRIPTION                                               | 23 |

|    | 6.1 AES3 and S/PDIF Standards Documents                           |    |

| 7. | SERIAL AUDIO OUTPUT PORT                                          | 23 |

|    | 7.1 Slip/Repeat Behavior                                          | 25 |

|    | 7.2 AES11 Behavior                                                | 26 |

| 8. | S/PDIF RECEIVER                                                   | 27 |

|    | 8.1 8:2 S/PDIF Input Multiplexer                                  | 27 |

|    | 8.1.1 General                                                     | 27 |

|    | 8.1.2 Software Mode                                               | 27 |

|    | 8.1.3 Hardware Mode                                               | 28 |

|    | 8.2 OMCK System Clock Mode                                        | 28 |

|    | 8.3 Clock Recovery and PLL Filter                                 |    |

| 9. | GENERAL PURPOSE OUTPUTS                                           |    |

| 10 | . ERROR AND STATUS REPORTING                                      | 30 |

|    | 10.1 General                                                      | 30 |

|    | 10.1.1 Software Mode                                              | 30 |

|    | 10.1.2 Hardware Mode                                              | 30 |

|    | 10.2 Non-Audio Detection                                          |    |

|    | 10.2.1 Format Detection                                           |    |

|    | 10.3 Interrupts                                                   |    |

| 11 | . CHANNEL STATUS AND USER-DATA HANDLING                           |    |

|    | 11.1 Software Mode                                                |    |

|    | 11.2 Hardware Mode                                                |    |

| 12 | . CONTROL PORT DESCRIPTION                                        |    |

| 14 | 12.1 SPI Mode                                                     |    |

|    | 12.1 °C Mode                                                      | -  |

| 12 | CONTROL PORT REGISTER QUICK REFERENCE                             |    |

|    | CONTROL PORT REGISTER GOICK REPERENCE                             |    |

| 14 | 14.1 Memory Address Pointer (MAP)                                 |    |

|    | 14.1 Memory Address Pointer (MAP)                                 |    |

|    |                                                                   |    |

|    | 14.3 Control1 (01h)                                               | ৩০ |

| 14.4 Control2 (02h)                                        | 39 |

|------------------------------------------------------------|----|

| 14.5 Control3 (03h)                                        | 40 |

| 14.6 Control4 (04h)                                        | 40 |

| 14.7 Serial Audio Data Format (05h)                        |    |

| 14.8 Receiver Error Mask (06h)                             |    |

| 14.9 Interrupt Mask (07h)                                  |    |

| 14.10 Interrupt Mode MSB (08h) and Interrupt Mode LSB(09h) | 42 |

| 14.11 Receiver Channel Status (0Ah)                        | 43 |

| 14.12 Format Detect Status (0Bh)                           | 43 |

| 14.13 Receiver Error (0Ch)                                 |    |

| 14.14 Interrupt 1 Status (0Dh)                             | 45 |

| 14.15 Q-Channel Subcode (0Eh - 17h)                        | 45 |

| 14.16 OMCK/RMCK Ratio (18h)                                |    |

| 14.17 Channel Status Registers (19h - 22h)                 | 46 |

| 14.18 IEC61937 PC/PD Burst Preamble (23h - 26h)            | 46 |

| 14.19 CS8416 I.D. and Version Register (7Fh)               | 46 |

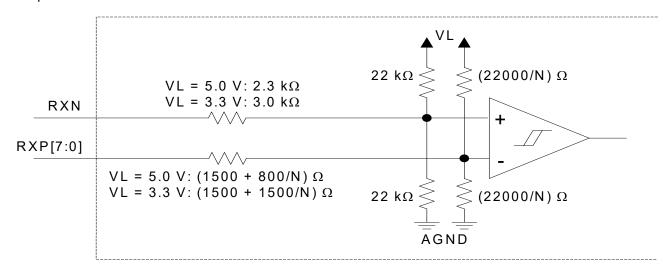

| 15. HARDWARE MODE                                          | 47 |

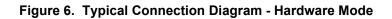

| 15.1 Serial Audio Port Formats                             | 47 |

| 15.2 Hardware Mode Function Selection                      | 47 |

| 15.3 Hardware Mode Equivalent Register Settings            |    |

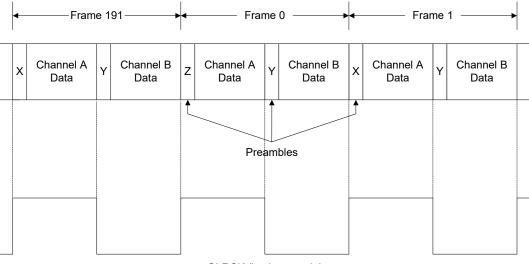

| 16. EXTERNAL AES3/SPDIF/IEC60958 RECEIVER COMPONENTS       |    |

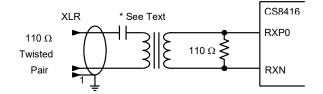

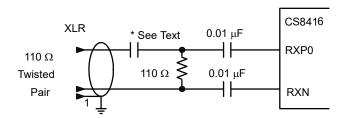

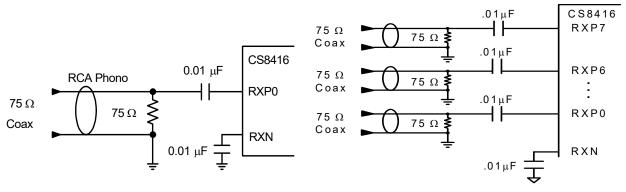

| 16.1 AES3 Receiver External Components                     | 50 |

| 16.2 Isolating Transformer Requirements                    |    |

| 17. CHANNEL STATUS BUFFER MANAGEMENT                       |    |

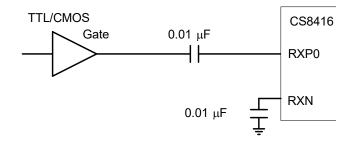

| 17.1 AES3 Channel Status (C) Bit Management                | 52 |

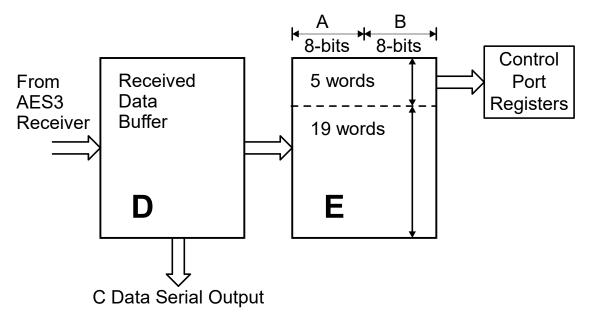

| 17.2 Accessing the E Buffer                                |    |

| 17.2.1 Serial Copy Management System (SCMS)                |    |

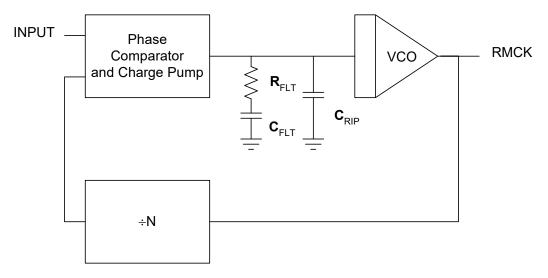

| 18. PLL FILTER                                             |    |

| 18.1 General                                               |    |

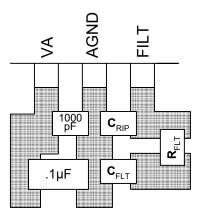

| 18.2 External Filter Components                            |    |

| 18.2.1 General                                             |    |

| 18.2.2 Capacitor Selection                                 |    |

| 18.2.3 Circuit Board Layout                                |    |

| 18.2.4 Component Value Selection                           |    |

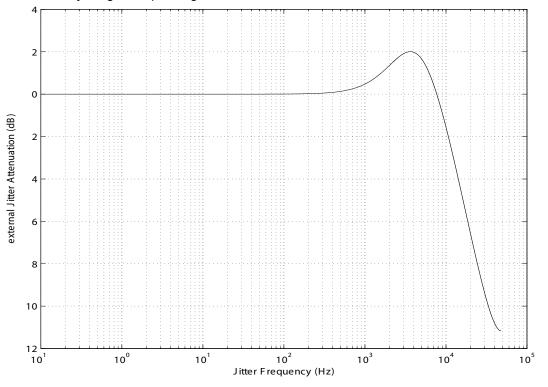

| 18.2.5 Jitter Attenuation                                  |    |

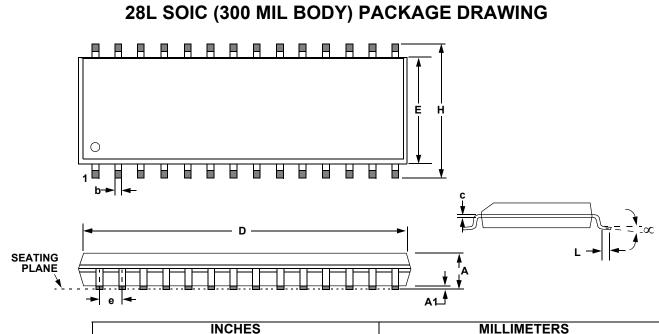

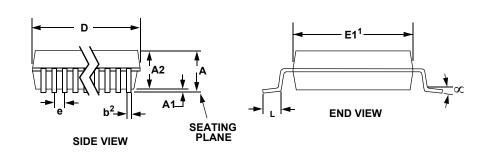

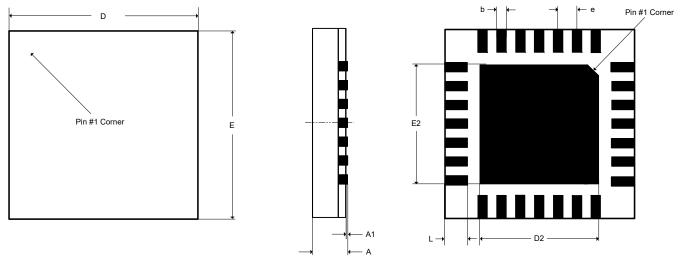

| 19. PACKAGE DIMENSIONS                                     | 57 |

| TSSOP THERMAL CHARACTERISTICS                              |    |

| QFN THERMAL CHARACTERISTICS                                |    |

| 20. ORDERING INFORMATION                                   |    |

|                                                            |    |

| 21. REVISION HISTORY                                       |    |

# CS8416

# LIST OF FIGURES

| Figure 1. Audio Port Master Mode Timing                           | 9  |

|-------------------------------------------------------------------|----|

| Figure 2. Audio Port Slave Mode and Data Input Timing             | 9  |

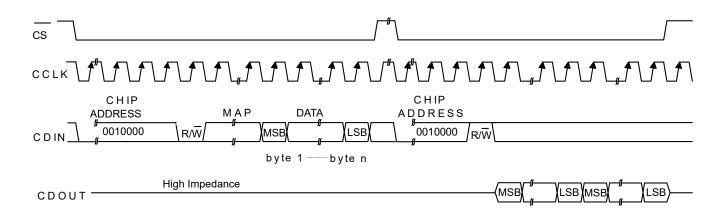

| Figure 3. SPI Mode Timing                                         | 10 |

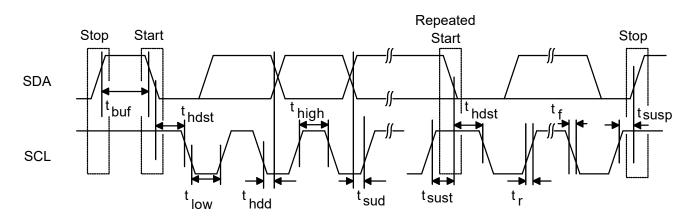

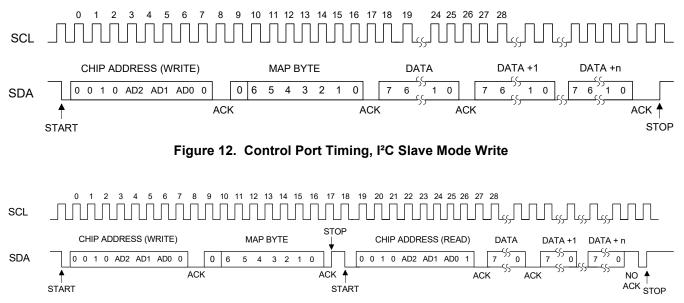

| Figure 4. I <sup>2</sup> C Mode Timing                            |    |

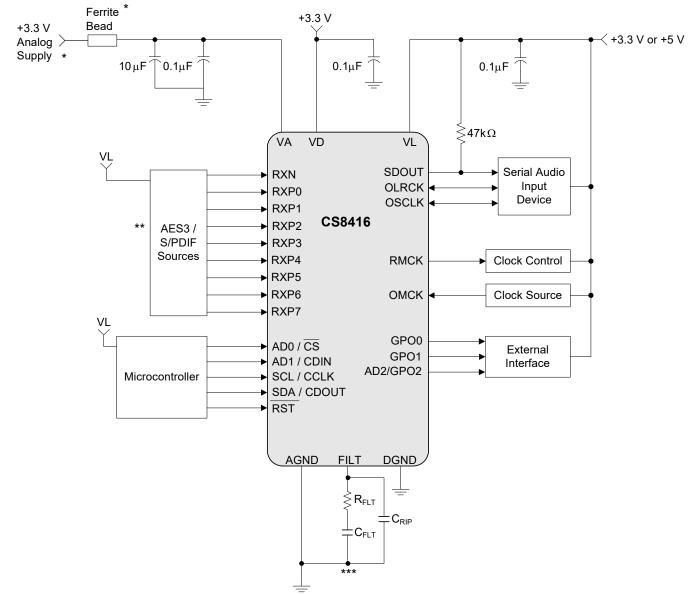

| Figure 5. Typical Connection Diagram - Software Mode              |    |

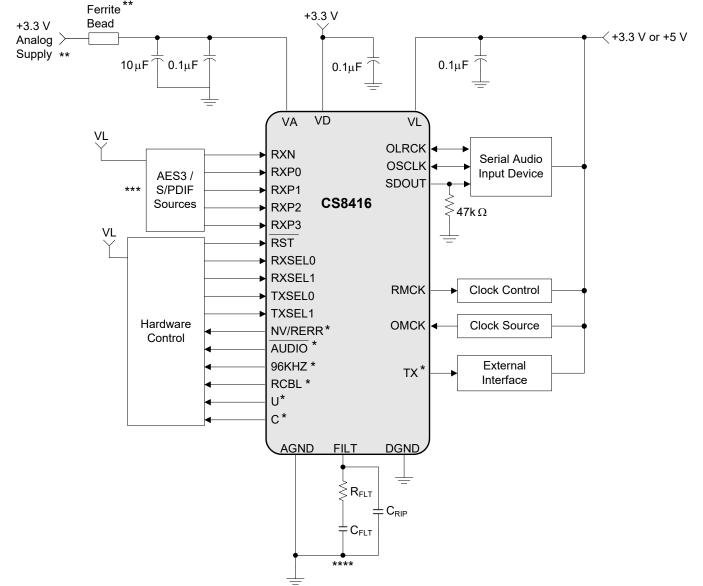

| Figure 6. Typical Connection Diagram - Hardware Mode              |    |

| Figure 7. Serial Audio Output Example Formats                     |    |

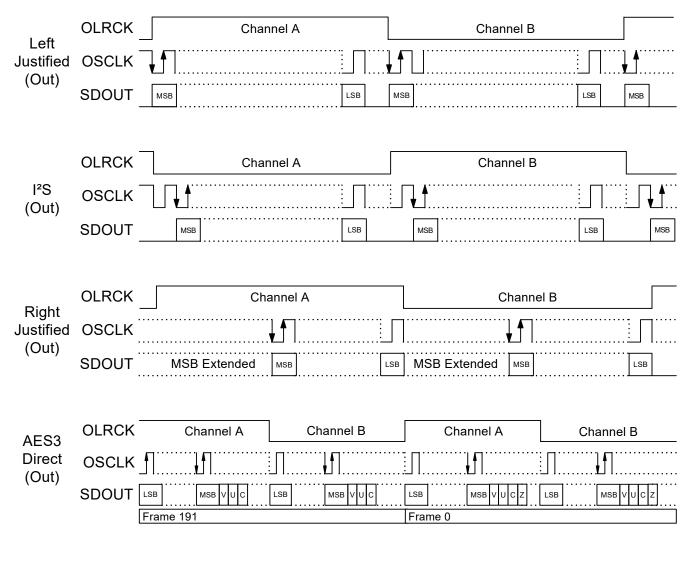

| Figure 8. AES3 Data Format                                        |    |

| Figure 9. Receiver Input Structure                                |    |

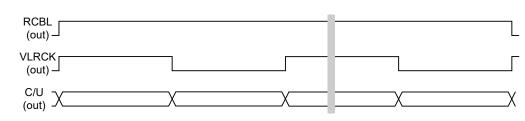

| Figure 10. C/U Data Outputs                                       |    |

| Figure 11. Control Port Timing in SPI Mode                        |    |

| Figure 12. Control Port Timing, I <sup>2</sup> C Slave Mode Write |    |

| Figure 13. Control Port Timing, I <sup>2</sup> C Slave Mode Read  |    |

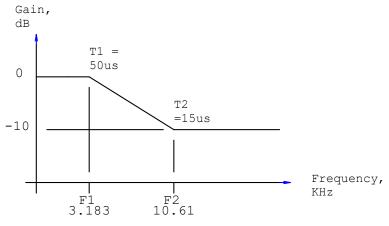

| Figure 14. De-Emphasis Filter Response                            |    |

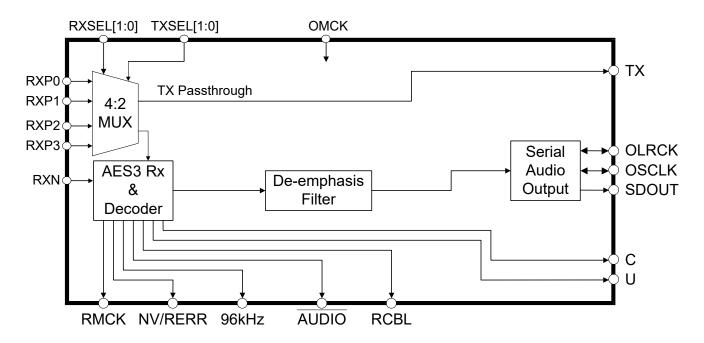

| Figure 15. Hardware Mode Data Flow                                |    |

| Figure 16. Professional Input Circuit                             |    |

| Figure 17. Transformerless Professional Input Circuit             |    |

| Figure 18. Consumer Input Circuit                                 |    |

| Figure 19. S/PDIF MUX Input Circuit                               |    |

| Figure 20. TTL/CMOS Input Circuit                                 |    |

| Figure 21. Channel Status Data Buffer Structure                   |    |

| Figure 22. Flowchart for Reading the E Buffer                     |    |

| Figure 23. PLL Block Diagram                                      |    |

| Figure 24. Recommended Layout Example                             |    |

| Figure 25. Jitter Attenuation Characteristics of PLL              | 56 |

## LIST OF TABLES

| Table 1. Typical Delays by Frequency Values       | 26 |

|---------------------------------------------------|----|

| Table 2. Clock Switching Output Clock Rates       | 28 |

| Table 3. GPO Pin Configurations                   |    |

| Table 4. Hardware Mode Start-Up Pin Conditions    | 48 |

| Table 5. Hardware Mode Serial Audio Format Select | 49 |

| Table 6. External PLL Component Values            | 55 |

### **1. CHARACTERISTICS AND SPECIFICATIONS**

All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and  $T_A = 25^{\circ}C$ .

## SPECIFIED OPERATING CONDITIONS

(AGND, DGND = 0 V, all voltages with respect to 0 V)

| Parameter                      |                                      | Symbol         | Min                  | Тур                      | Max                  | Units |

|--------------------------------|--------------------------------------|----------------|----------------------|--------------------------|----------------------|-------|

| Power Supply Voltage           |                                      | VA<br>VD<br>VL | 3.13<br>3.13<br>3.13 | 3.3<br>3.3<br>3.3 or 5.0 | 3.46<br>3.46<br>5.25 | < < < |

| Ambient Operating Temperature: | Commercial Grade<br>Automotive Grade |                | -10<br>-40           | -                        | +70<br>+85           | °C    |

### ABSOLUTE MAXIMUM RATINGS

(AGND, DGND = 0 V; all voltages with respect to 0 V. Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.)

| Parameter                                       | Symbol           | Min  | Max        | Units |

|-------------------------------------------------|------------------|------|------------|-------|

| Power Supply Voltage                            | VA, VD,VL        | -    | 6.0        | V     |

| Input Current, Any Pin Except Supplies (Note 1) | l <sub>in</sub>  | -    | ±10        | mA    |

| Input Voltage                                   | V <sub>in</sub>  | -0.3 | (VL) + 0.3 | V     |

| Ambient Operating Temperature (power applied)   | T <sub>A</sub>   | -55  | 125        | °C    |

| Storage Temperature                             | T <sub>stg</sub> | -65  | 150        | °C    |

Notes:

1. Transient currents of up to 100 mA will not cause SCR latch-up.

# DC ELECTRICAL CHARACTERISTICS

(AGND = DGND = 0 V; all voltages with respect to 0 V.)

| Parameters                           |            | Symbol | Min | Тур  | Max | Units |

|--------------------------------------|------------|--------|-----|------|-----|-------|

| Power-Down Mode (Notes 2, 4)         |            |        | I.  |      |     |       |

| Supply Current in power-down         | VA         | IA     | -   | 10   | -   | μA    |

|                                      | VD         | ID     | -   | 70   | -   | μA    |

|                                      | VL = 3.3 V | IL     | -   | 10   | -   | μA    |

|                                      | VL = 5.0 V | IL     | -   | 12   | -   | μA    |

| Normal Operation (Notes 3, 4)        |            |        | •   |      | •   |       |

| Supply Current at 48 kHz frame rate  | VA         | IA     | -   | 5.7  | -   | mA    |

|                                      | VD         | ID     | -   | 5.9  | -   | mA    |

|                                      | VL = 3.3 V | IL     | -   | 2.8  | -   | mA    |

|                                      | VL = 5.0 V | IL     | -   | 4.2  | -   | mA    |

| Supply Current at 192 kHz frame rate | VA         | IA     | -   | 9.4  | -   | mA    |

|                                      | VD         | ID     | -   | 23   | -   | mA    |

|                                      | VL = 3.3 V | IL     | -   | 7.8  | -   | mA    |

|                                      | VL = 5.0 V | IL     | -   | 11.8 | -   | mA    |

Notes:

- 2. Power-Down Mode is defined as  $\overline{RST}$  = LO with all clocks and data lines held static.

- 3. Normal operation is defined as  $\overline{RST} = HI$ .

- 4. Assumes that no inputs are floating. It is recommended that all inputs be driven high or low at all times.

### **DIGITAL INPUT CHARACTERISTICS**

(AGND = DGND = 0 V; all voltages with respect to 0 V.)

| Parameters                                      | Symbol          | Min  | Тур | Max  | Units |

|-------------------------------------------------|-----------------|------|-----|------|-------|

| Input Leakage Current                           | I <sub>IN</sub> | -    | -   | ±0.5 | μA    |

| Differential Input Sensitivity, RXP[7:0] to RXN | V <sub>TH</sub> | -    | 150 | 200  | mVpp  |

| Input Hysteresis                                | V <sub>H</sub>  | 0.15 | -   | 1.0  | V     |

### **DIGITAL INTERFACE SPECIFICATIONS**

(AGND = DGND = 0 V; all voltages with respect to 0 V.)

| Parameters                                            | Symbol          | Min        | Max        | Units |

|-------------------------------------------------------|-----------------|------------|------------|-------|

| High-Level Output Voltage (I <sub>OH</sub> = -3.2 mA) | V <sub>OH</sub> | (VL) - 1.0 | -          | V     |

| Low-Level Output Voltage (I <sub>OL</sub> = 3.2 mA)   | V <sub>OL</sub> | -          | 0.5        | V     |

| High-Level Input Voltage, except RXP[7:0], RXN        | V <sub>IH</sub> | 2.0        | (VL) + 0.3 | V     |

| Low-Level Input Voltage, except RXP[7:0], RXN         | V <sub>IL</sub> | -0.3       | 0.8        | V     |

### **SWITCHING CHARACTERISTICS**

(Inputs: Logic 0 = 0 V, Logic 1 = VL;  $C_L$  = 20 pF)

| Parameter                 |                      | Symbol | Min      | Тур      | Max      | Units  |

|---------------------------|----------------------|--------|----------|----------|----------|--------|

| RST Pin Lov               | v Pulse Width        |        | 200      | -        | -        | μS     |

| PLL Clock Recovery Sample | e Rate Range         |        | 30       | -        | 200      | kHz    |

| RMCK Output Jitter        | (Note 5)             |        | -        | 200      | -        | ps RMS |

| RMCK Output Duty-Cycle    | (Note 6)<br>(Note 7) |        | 45<br>50 | 50<br>55 | 55<br>65 | %<br>% |

| RMCK/OMCK Maximum Freque  | ncy                  |        | -        | -        | 50       | MHz    |

#### Notes:

- 5. Typical RMS cycle-to-cycle jitter.

- 6. Duty cycle when clock is recovered from biphase encoded input.

- 7. Duty cycle when OMCK is switched over for output on RMCK.

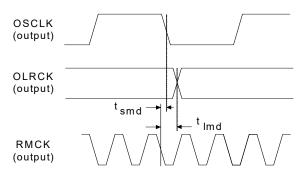

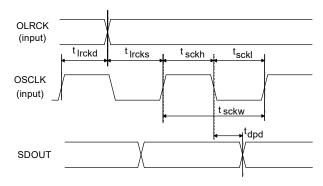

### **SWITCHING CHARACTERISTICS - SERIAL AUDIO PORTS**

(Inputs: Logic 0 = 0 V, Logic 1 = VL;  $C_L = 20$  pF)

| Parameter                                     |              | Symbol             | Min | Тур | Max | Units |

|-----------------------------------------------|--------------|--------------------|-----|-----|-----|-------|

| OSCLK/OLRCK Active Edge to SDOUT Output Valid | (Note 8)     | t <sub>dpd</sub>   | -   | -   | 23  | ns    |

| Master Mode                                   |              |                    |     |     |     |       |

| RMCK to OSCLK active edge delay               | (Note 8)     | t <sub>smd</sub>   | 0   | -   | 12  | ns    |

| RMCK to OLRCK delay                           | (Note 9)     | t <sub>lmd</sub>   | 0   | -   | 12  | ns    |

| OSCLK and OLRCK Duty Cycle                    |              |                    | -   | 50  | -   | %     |

| Slave Mode                                    |              |                    |     |     |     |       |

| OSCLK Period                                  |              | t <sub>sckw</sub>  | 36  | -   | -   | ns    |

| OSCLK Input Low Width                         |              | t <sub>sckl</sub>  | 14  | -   | -   | ns    |

| OSCLK Input High Width                        |              | t <sub>sckh</sub>  | 14  | -   | -   | ns    |

| OSCLK Active Edge to OLRCK Edge (No           | otes 8,9,10) | t <sub>lrckd</sub> | 10  | -   | -   | ns    |

| OSCLK Edge Setup Before OSCLK Active-Edge (No | otes 8,9,11) | t <sub>lrcks</sub> | 10  | -   | -   | ns    |

Notes:

- 8. In Software Mode the active edges of OSCLK are programmable.

- 9. In Software Mode the polarity of OLRCK is programmable.

- 10. This delay is to prevent the previous OSCLK edge from being interpreted as the first one after OLRCK has changed.

- 11. This setup time ensures that this OSCLK edge is interpreted as the first one after OLRCK has changed.

Figure 1. Audio Port Master Mode Timing

Figure 2. Audio Port Slave Mode and Data Input

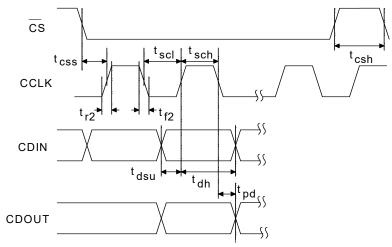

# SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MODE

(Inputs: Logic 0 = 0 V, Logic 1 = VL;  $C_L = 20$  pF)

| Parameter                                    | Symbol           | Min | Max | Unit |

|----------------------------------------------|------------------|-----|-----|------|

| CCLK Clock Frequency (Note 12)               | f <sub>sck</sub> | 0   | 6.0 | MHz  |

| CS High Time Between Transmissions           | t <sub>csh</sub> | 1.0 | -   | μs   |

| CS Falling to CCLK Edge                      | t <sub>css</sub> | 20  | -   | ns   |

| CCLK Low Time                                | t <sub>scl</sub> | 66  | -   | ns   |

| CCLK High Time                               | t <sub>sch</sub> | 66  | -   | ns   |

| CDIN to CCLK Rising Setup Time               | t <sub>dsu</sub> | 40  | -   | ns   |

| CCLK Rising to DATA Hold Time (Note 13)      | t <sub>dh</sub>  | 15  | -   | ns   |

| CCLK Falling to CDOUT Stable                 | t <sub>pd</sub>  | -   | 50  | ns   |

| Rise Time of CDOUT                           | t <sub>r1</sub>  | -   | 25  | ns   |

| Fall Time of CDOUT                           | t <sub>f1</sub>  | -   | 25  | ns   |

| Rise Time of CCLK and CDIN (Note 14)         | t <sub>r2</sub>  | -   | 100 | ns   |

| Fall Time of CCLK and CDIN         (Note 14) | t <sub>r2</sub>  | -   | 100 | ns   |

#### Notes:

- 12. If Fs is lower than 46.875 kHz, the maximum CCLK frequency should be less than 128 Fs. This is dictated by the timing requirements necessary to access the Channel Status memory. Access to the control register file can be carried out at the full 6 MHz rate. The minimum allowable input sample rate is 32 kHz, so choosing CCLK to be less than or equal to 4.1 MHz should be safe for all possible conditions.

- 13. Data must be held for sufficient time to bridge the transition time of CCLK.

- 14. For f<sub>sck</sub> <1 MHz.

Figure 3. SPI Mode Timing

# SWITCHING CHARACTERISTICS - CONTROL PORT- I<sup>2</sup>C FORMAT

(Inputs: Logic 0 = 0 V, Logic 1 = VL;  $C_L = 20$  pF)

| Parameter                                              | Symbol            | Min | Max  | Unit |

|--------------------------------------------------------|-------------------|-----|------|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -   | 100  | kHz  |

| Bus Free Time Between Transmissions                    | t <sub>buf</sub>  | 4.7 | -    | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 4.0 | -    | μs   |

| Clock Low time                                         | t <sub>low</sub>  | 4.7 | -    | μs   |

| Clock High Time                                        | t <sub>high</sub> | 4.0 | -    | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 4.7 | -    | μs   |

| SDA Hold Time from SCL Falling (Note 15)               | t <sub>hdd</sub>  | 10  | -    | ns   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>  | 250 | -    | ns   |

| Rise Time of SCL and SDA                               | t <sub>r</sub>    | -   | 1000 | ns   |

| Fall Time SCL and SDA                                  | t <sub>f</sub>    | -   | 300  | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 4.7 | -    | μs   |

#### Notes:

15. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.

### 2. PIN DESCRIPTION - SOFTWARE MODE

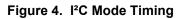

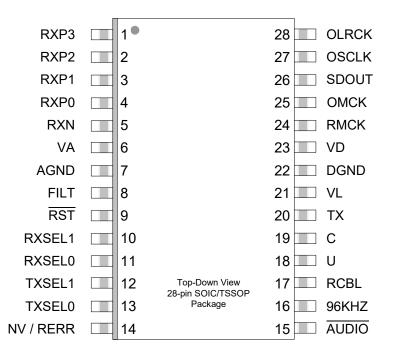

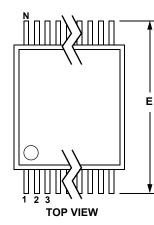

### 2.1 TSSOP Pin Description

| Pin<br>Name | Pin # | Pin Description                                                                                                                                                                                                                                                                             |  |  |  |  |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VA          | 6     | <b>Analog Power</b> ( <i>Input</i> ) - Analog power supply. Nominally +3.3 V. This supply should have as little noise as possible since noise on this pin will directly affect the jitter performance of the recovered clock                                                                |  |  |  |  |

| VD          | 23    | Digital Power (Input) – Digital core power supply. Nominally +3.3 V                                                                                                                                                                                                                         |  |  |  |  |

| VL          | 21    | Logic Power (Input) – Input/Output power supply. Nominally +3.3 V or +5.0 V                                                                                                                                                                                                                 |  |  |  |  |

| AGND        | 7     | <b>Analog Ground</b> ( <i>Input</i> ) - Ground for the analog circuitry in the chip. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                              |  |  |  |  |

| DGND        | 22    | <b>Digital &amp; I/O Ground</b> ( <i>Input</i> ) - Ground for the I/O and core logic. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                             |  |  |  |  |

| RST         | 9     | <b>Reset</b> ( <i>Input</i> ) - When RST is low, the CS8416 enters a low power mode and all internal states are reset.<br>On initial power up, RST must be held low until the power supply is stable, and all input clocks are stable in frequency and phase.                               |  |  |  |  |

| FILT        | 8     | PLL Loop Filter ( <i>Output</i> ) - An RC network should be connected between this pin and analog ground.<br>For minimum PLL jitter, return the ground end of the filter network directly to AGND. See "PLL Filter" on page 54 for more information on the PLL and the external components. |  |  |  |  |

| RXP0        | 4     |                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RXP1        | 3     | Positive AES3/SPDIF Input (Input) - Single-ended or differential receiver inputs carrying AES3 or                                                                                                                                                                                           |  |  |  |  |

| RXP2        | 2     | S/PDIF encoded digital data. The RXP[7:0] inputs comprise the 8:2 S/PDIF Input Multiplexer. The select                                                                                                                                                                                      |  |  |  |  |

| RXP3        | 1     | line control is accessed using the Control 4 register (04h). Unused multiplexer inputs should be left float-                                                                                                                                                                                |  |  |  |  |

| RXP4        | 10    | ing or tied to AGND. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for re<br>ommended input circuits.                                                                                                                                                                   |  |  |  |  |

| RXP5        | 11    |                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RXP6        | 12    |                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RXP7        | 13    |                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Pin            | Pin # | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name           |       |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

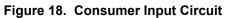

| RXN            | 5     | <b>Negative AES3/SPDIF Input</b> ( <i>Input</i> ) - Single-ended or differential receiver input carrying AES3 or S/PDIF encoded digital data. Used along with RXP[7:0] to form an AES3 differential input. In single-ended operation this should be AC coupled to ground through a capacitor. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for recommended input circuits.                         |  |  |  |

| ОМСК           | 25    | <b>System Clock</b> ( <i>Input</i> ) - When the OMCK System Clock Mode is enabled using the SWCLK bit in the Control 1 register, the clock signal input on this pin is automatically output through RMCK on PLL unlock. OMCK serves as the reference signal for OMCK/RMCK ratio expressed in register 18h. "OMCK System Clock Mode" section on page 28                                                                  |  |  |  |

| RMCK           | 24    | <b>Input Section Recovered Master Clock</b> ( <i>Output</i> ) - Input section recovered master clock output from the PLL. Frequency defaults to 256x the sample rate ( $F_s$ ) and may be set to 128x through the RMCKF bit in the Control 1 register (01h). RMCK may also be set to high impedance by the RXD bit in the Control 4 register (04h).                                                                     |  |  |  |

| OSCLK          | 27    | Serial Audio Output Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin                                                                                                                                                                                                                                                                                                                         |  |  |  |

| OLRCK          | 28    | Serial Audio Output Left/Right Clock ( <i>Input/Output</i> ) - Word rate clock for the audio data on the SDOUT pin. Frequency will be the output sample rate (Fs)                                                                                                                                                                                                                                                       |  |  |  |

| SDOUT          | 26    | <b>Serial Audio Output Data</b> ( <i>Output</i> ) - Audio data serial output pin. This pin must be pulled high to VL through a 47 k $\Omega$ resistor to place the part in Software Mode.                                                                                                                                                                                                                               |  |  |  |

| SDA /<br>CDOUT | 17    | Serial Control Data I/O (I <sup>2</sup> C) / Data Out (SPI) ( <i>Input/Output</i> ) - In I <sup>2</sup> C Mode, SDA is the control I/O data line. SDA is open drain and requires an external pull-up resistor to VL. In SPI Mode, CDOUT is the output data from the control port interface on the CS8416. See the "Control Port Description" section on page 34.                                                        |  |  |  |

| SCL /<br>CCLK  | 16    | <b>Control Port Clock</b> ( <i>Input</i> ) - Serial control interface clock and is used to clock control data bits into and out of the CS8416. CCLK is an open drain output and requires an external pull-up resistor to VL. See the "Control Port Description" section on page 34.                                                                                                                                     |  |  |  |

| AD0 / CS       | 14    | Address Bit 0 (I <sup>2</sup> C) / Control Port Chip Select (SPI) ( <i>Input</i> ) - A falling edge on this pin puts the CS8416 into SPI Control Port Mode. With no falling edge, the CS8416 defaults to I <sup>2</sup> C Mode. In I <sup>2</sup> C Mode, AD0 is a chip address pin. In SPI Mode, CS is used to enable the control port interface on the CS8416. See the "Control Port Description" section on page 34. |  |  |  |

| AD1 /<br>CDIN  | 15    | Address Bit 1 (I <sup>2</sup> C) / Serial Control Data in (SPI) ( <i>Input</i> ) - In I <sup>2</sup> C Mode, AD1 is a chip address pin. In SPI Mode, CDIN is the input data line for the control port interface. See the "Control Port Description" section on page 34.                                                                                                                                                 |  |  |  |

| AD2 /<br>GPO2  | 18    | <b>General Purpose Output 2</b> ( <i>Output</i> ) - If using the I <sup>2</sup> C control port, this pin must be pulled high or low through a 47 k $\Omega$ resistor. See the "Control Port Description" section on page 34 and "General Purpose Outputs" on page 29 for GPO functions.                                                                                                                                 |  |  |  |

| GPO1           | 19    | General Purpose Output 1 (Output) - See "General Purpose Outputs" on page 29 for GPO functions.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| GPO0           | 20    | General Purpose Output 0 (Output) - See "General Purpose Outputs" on page 29 for GPO functions.                                                                                                                                                                                                                                                                                                                         |  |  |  |

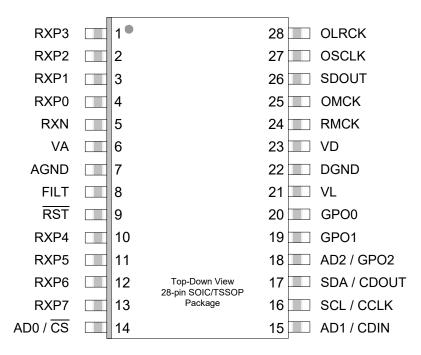

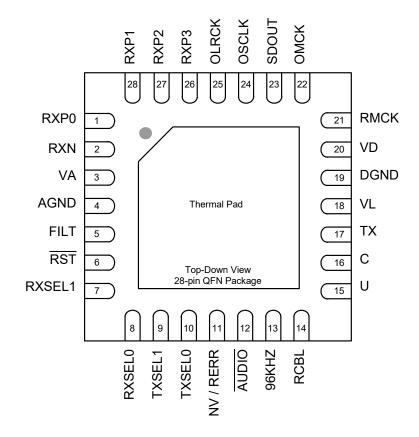

### 2.2 QFN Pin Description

| Pin<br>Name | Pin # | Pin Description                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VA          | 3     | <b>nalog Power</b> ( <i>Input</i> ) - Analog power supply. Nominally +3.3 V. This supply should have as little noise s possible since noise on this pin will directly affect the jitter performance of the recovered clock                                                                          |  |  |  |

| VD          | 20    | Digital Power (Input) – Digital core power supply. Nominally +3.3 V                                                                                                                                                                                                                                 |  |  |  |

| VL          | 18    | Logic Power (Input) – Input/Output power supply. Nominally +3.3 V or +5.0 V                                                                                                                                                                                                                         |  |  |  |

| AGND        | 4     | <b>Analog Ground</b> ( <i>Input</i> ) - Ground for the analog circuitry in the chip. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                                      |  |  |  |

| DGND        | 19    | <b>Digital &amp; I/O Ground</b> ( <i>Input</i> ) - Ground for the I/O and core logic. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                                     |  |  |  |

| RST         | 6     | <b>Reset</b> ( <i>Input</i> ) - When $\overrightarrow{RST}$ is low, the CS8416 enters a low power mode and all internal states are reset.<br>On initial power up, $\overrightarrow{RST}$ must be held low until the power supply is stable, and all input clocks are stable in frequency and phase. |  |  |  |

| FILT        | 5     | <b>PLL Loop Filter</b> ( <i>Output</i> ) - An RC network should be connected between this pin and analog ground.<br>For minimum PLL jitter, return the ground end of the filter network directly to AGND. See "PLL Filter" on page 54 for more information on the PLL and the external components.  |  |  |  |

| Pin            | Pin # | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name           |       |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RXP0           | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RXP1           | 28    | Positive AES3/SPDIF Input (Input) - Single-ended or differential receiver inputs carrying AES3 or                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| RXP2           | 27    |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RXP3           | 26    | S/PDIF encoded digital data. The RXP[7:0] inputs comprise the 8:2 S/PDIF Input Multiplexer. The select                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| RXP4           | 7     | line control is accessed using the Control 4 register (04h). Unused multiplexer inputs should be left float-                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| RXP5           | 8     | ing or tied to AGND. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for rec-                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RXP6           | 9     | ommended input circuits.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| RXP7           | 10    |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                | 10    |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RXN            | 2     | <b>legative AES3/SPDIF Input</b> ( <i>Input</i> ) - Single-ended or differential receiver input carrying AES3 or<br>S/PDIF encoded digital data. Used along with RXP[7:0] to form an AES3 differential input. In single-<br>nded operation this should be AC coupled to ground through a capacitor. See "External<br>SS3/SPDIF/IEC60958 Receiver Components" on page 50 for recommended input circuits.                 |  |  |  |  |  |

| ОМСК           | 22    | <b>System Clock</b> ( <i>Input</i> ) - When the OMCK System Clock Mode is enabled using the SWCLK bit in the Control 1 register, the clock signal input on this pin is automatically output through RMCK on PLL unlock. OMCK serves as the reference signal for OMCK/RMCK ratio expressed in register 18h. "OMCK System Clock Mode" section on page 28                                                                  |  |  |  |  |  |

|                |       | Input Section Recovered Master Clock (Output) - Input section recovered master clock output from                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| RMCK           | 21    | the PLL. Frequency defaults to 256x the sample rate (F <sub>s</sub> ) and may be set to 128x through the RMCKF bit                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RIVICK         | 21    | in the Control 1 register (01h). RMCK may also be set to high impedance by the RXD bit in the Control 4                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                |       | register (04h).                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| OSCLK          | 24    | Serial Audio Output Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| OLRCK          | 25    | Serial Audio Output Left/Right Clock ( <i>Input/Output</i> ) - Word rate clock for the audio data on the SDOUT pin. Frequency will be the output sample rate (Fs)                                                                                                                                                                                                                                                       |  |  |  |  |  |

| SDOUT          | 23    | Serial Audio Output Data ( <i>Output</i> ) - Audio data serial output pin. This pin must be pulled high to VL through a 47 k $\Omega$ resistor to place the part in Software Mode.                                                                                                                                                                                                                                      |  |  |  |  |  |

|                |       | Serial Control Data I/O (I <sup>2</sup> C) / Data Out (SPI) (Input/Output) - In I <sup>2</sup> C Mode, SDA is the control I/O data                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| SDA /<br>CDOUT | 14    | line. SDA is open drain and requires an external pull-up resistor to VL. In SPI Mode, CDOUT is the output data from the control port interface on the CS8416. See the "Control Port Description" section on page 34.                                                                                                                                                                                                    |  |  |  |  |  |

|                |       | Control Port Clock (Input) - Serial control interface clock and is used to clock control data bits into and                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| SCL/           | 13    | out of the CS8416. CCLK is an open drain output and requires an external pull-up resistor to VL. See the                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| CCLK           |       | "Control Port Description" section on page 34.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD0 / CS       | 11    | Address Bit 0 (I <sup>2</sup> C) / Control Port Chip Select (SPI) ( <i>Input</i> ) - A falling edge on this pin puts the CS8416 into SPI Control Port Mode. With no falling edge, the CS8416 defaults to I <sup>2</sup> C Mode. In I <sup>2</sup> C Mode, AD0 is a chip address pin. In SPI Mode, CS is used to enable the control port interface on the CS8416. See the "Control Port Description" section on page 34. |  |  |  |  |  |

|                |       | Address Bit 1 (I <sup>2</sup> C) / Serial Control Data in (SPI) (Input) - In I <sup>2</sup> C Mode, AD1 is a chip address pin. In                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| AD1 /<br>CDIN  | 12    | SPI Mode, CDIN is the input data line for the control port interface. See the "Control Port Description" section on page 34.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                |       | General Purpose Output 2 (Output) - If using the I <sup>2</sup> C control port, this pin must be pulled high or low                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| AD2 /          | 15    | through a 47 kΩ resistor. See the "Control Port Description" section on page 34 and "General Purpose                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| GPO2           | -     | Outputs" on page 29 for GPO functions.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| GPO1           | 16    | General Purpose Output 1 (Output) - See "General Purpose Outputs" on page 29 for GPO functions.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| GPO0           | 10    | General Purpose Output 0 (Output) - See "General Purpose Outputs" on page 29 for GPO functions.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                |       |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| THERMAL<br>PAD | -     | Thermal Pad - Thermal relief pad for optimized heat dissipation.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

### 3. PIN DESCRIPTION - HARDWARE MODE

### 3.1 **TSSOP Pin Description**

| Pin Name                     | Pin #            | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VA                           | 6                | <b>Analog Power</b> ( <i>Input</i> ) - Analog power supply. Nominally +3.3 V. This supply should have as little noise as possible since noise on this pin will directly affect the jitter performance of the recovered clock                                                                                                                                                                                                                       |  |  |

| VD                           | 23               | Digital Power (Input) – Digital core power supply. Nominally +3.3 V                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VL                           | 21               | Logic Power (Input) – Input/Output power supply. Nominally +3.3 V or +5.0 V                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| AGND                         | 7                | <b>Analog Ground</b> ( <i>Input</i> ) - Ground for the analog circuitry in the chip. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                                                                                                                                                                                     |  |  |

| DGND                         | 22               | <b>Digital &amp; I/O Ground</b> ( <i>Input</i> ) - Ground for the I/O and core logic. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                                                                                                                                                                                    |  |  |

| RST                          | 9                | <b>Reset</b> ( <i>Input</i> ) - When RST is low, the CS8416 enters a low power mode and all internal states are reset. On initial power up, RST must be held low until the power supply is stable, and all input clocks are stable in frequency and phase.                                                                                                                                                                                         |  |  |

| FILT                         | 8                | <b>PLL Loop Filter</b> ( <i>Output</i> ) - An RC network should be connected between this pin and analog ground.<br>For minimum PLL jitter, return the ground end of the filter network directly to AGND. See "PLL Filter on page 54 for more information on the PLL and the external components.                                                                                                                                                  |  |  |

| RXP0<br>RXP1<br>RXP2<br>RXP3 | 4<br>3<br>2<br>1 | <b>Positive AES3/SPDIF Input</b> ( <i>Input</i> ) - Single-ended or differential receiver inputs carrying AES3 or S/PDIF encoded digital data. The RXP[3:0] inputs comprise the 4:2 S/PDIF Input Multiplexer. The select line control is accessed using the RXPSEL[1:0] pins. Unused multiplexer inputs should be left floating or tied to AGND. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for recommended input circuits. |  |  |

| RXN                          | 5                | <b>Negative AES3/SPDIF Input</b> ( <i>Input</i> ) - Single-ended or differential receiver input carrying AES3 or S/PDIF encoded digital data. Used along with RXP[3:0] to form an AES3 differential input. In single-ended operation this should be AC coupled to ground through a capacitor. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for recommended input circuits.                                                    |  |  |

| Pin Name         | Pin #    | Pin Description                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ОМСК             | 25       | <b>System Clock</b> ( <i>Input</i> ) - OMCK System Clock Mode is enabled by a transition (rising edge active) on OMCK after reset. When enabled, the clock signal input on this pin is automatically output through RMCK on PLL unlock. See "OMCK System Clock Mode" on page 28.                                                                                             |  |  |

| RMCK             | 24       | <b>Input Section Recovered Master Clock</b> ( <i>Output</i> ) - Input section recovered master clock output from the PLL. Frequency is 256x the sample rate ( $F_s$ ) when the U pin is pulled down by a 47 k $\Omega$ resistor to DGND. Frequency is 128x the sample rate ( $F_s$ ) when the U pin is pulled up by a 47 k $\Omega$ resistor to VL.                          |  |  |

| OSCLK            | 27       | Serial Audio Output Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin                                                                                                                                                                                                                                                                              |  |  |

| OLRCK            | 28       | Serial Audio Output Left/Right Clock ( <i>Input/Output</i> ) - Word rate clock for the audio data on the SDOUT pin. Frequency will be the output sample rate (Fs)                                                                                                                                                                                                            |  |  |

| SDOUT            | 26       | <b>Serial Audio Output Data</b> ( <i>Output</i> ) - Audio data serial output pin. This pin must be pulled low to DGND through a 47 k $\Omega$ resistor to place the part in Hardware Mode.                                                                                                                                                                                   |  |  |

| RXSEL1<br>RXSEL0 | 10<br>11 | Receiver MUX Selector (Input) - Used to select which pin, RXP[3:0], is used for the receiver input.                                                                                                                                                                                                                                                                          |  |  |

| TXSEL1<br>TXSEL0 | 12<br>13 | <b>TX Pin MUX SELECTION</b> ( <i>Input</i> ) - Used to select which pin, RXP[3:0], is passed to the TX pin output. If TX passthrough is not used, the user should set it to output one of the unused receiver inputs.                                                                                                                                                        |  |  |

| ТХ               | 20       | <b>S/PDIF MUX Passthrough</b> ( <i>Output</i> ) - Single-ended signal is resolved to full-rail, but is not de-jittered before it is output. Output is set by TXSEL[1:0]. This pin is also used to select the type of phase detector (PDUR) at reset. If TX passthrough is not used, the user should set it to output one of the unused receiver inputs.                      |  |  |

| NV/RERR          | 14       | <b>Non-Validity Receiver Error/Receiver Error</b> ( <i>Output</i> ) - Receiver error indicator. NVERR is selected by a 47 k $\Omega$ resistor to DGND. RERR is selected by a 47 k $\Omega$ resistor to VL.                                                                                                                                                                   |  |  |

| AUDIO            | 15       | Audio Channel Status Bit ( <i>Output</i> ) – When low, a valid linear PCM audio stream is indicated. See<br>"Non-Audio Detection" on page 31. This pin is also used to select the serial port format (SFSEL1) at reset.                                                                                                                                                      |  |  |

| 96KHZ            | 16       | <b>96 kHz Sample Rate Detect</b> ( <i>Output</i> ) - If the input sample rate is $\leq$ 48 kHz, outputs a "0". Outputs a "1" if the sample rate is $\geq$ 88.1 kHz. Otherwise the output is indeterminate. Also used to set the Emphasis Audio Match feature at reset.                                                                                                       |  |  |

| RCBL             | 17       | Receiver Channel Status Block <i>(Output)</i> -Indicates the beginning of a received channel status block.<br>RCBL goes high two frames after the reception of a Z preamble, remains high for 16 frames and then<br>returns low for the remainder of the block. RCBL changes on rising edges of RMCK. Also used to set<br>the serial audio port to master or slave at reset. |  |  |

| С                | 19       | <b>Channel Status Data</b> ( <i>Output</i> ) - Outputs channel status data from the AES3 receiver, clocked by the rising and falling edges of OLRCK. Also used to select the serial port format (SFSEL0) at reset.                                                                                                                                                           |  |  |

| U                | 18       | <b>User Data</b> ( <i>Output</i> ) - Outputs user data from the AES3 receiver, clocked by the rising and falling edges of OLRCK. Also used to select the frequency of RMCK to either $256*F_s$ or $128*F_s$ at reset.                                                                                                                                                        |  |  |

### 3.2 QFN Pin Description

| Pin Name                     | Pin #               | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VA                           | 3                   | <b>Analog Power</b> ( <i>Input</i> ) - Analog power supply. Nominally +3.3 V. This supply should have as little noise as possible since noise on this pin will directly affect the jitter performance of the recovered clock                                                                                                                                                                                                                       |  |  |  |

| VD                           | 20                  | Digital Power (Input) – Digital core power supply. Nominally +3.3 V                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| VL                           | 18                  | Logic Power (Input) – Input/Output power supply. Nominally +3.3 V or +5.0 V                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| AGND                         | 4                   | <b>Analog Ground</b> ( <i>Input</i> ) - Ground for the analog circuitry in the chip. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                                                                                                                                                                                     |  |  |  |

| DGND                         | 19                  | <b>Digital &amp; I/O Ground</b> ( <i>Input</i> ) - Ground for the I/O and core logic. AGND and DGND should be connected to a common ground area under the chip.                                                                                                                                                                                                                                                                                    |  |  |  |

| RST                          | 6                   | <b>Reset</b> ( <i>Input</i> ) - When $\overrightarrow{\text{RST}}$ is low, the CS8416 enters a low power mode and all internal states are reset. On initial power up, $\overrightarrow{\text{RST}}$ must be held low until the power supply is stable, and all input clocks are stable in frequency and phase.                                                                                                                                     |  |  |  |

| FILT                         | 5                   | PLL Loop Filter ( <i>Output</i> ) - An RC network should be connected between this pin and analog ground.<br>For minimum PLL jitter, return the ground end of the filter network directly to AGND. See "PLL Filter" on page 54 for more information on the PLL and the external components.                                                                                                                                                        |  |  |  |

| RXP0<br>RXP1<br>RXP2<br>RXP3 | 1<br>28<br>27<br>26 | <b>Positive AES3/SPDIF Input</b> ( <i>Input</i> ) - Single-ended or differential receiver inputs carrying AES3 or S/PDIF encoded digital data. The RXP[3:0] inputs comprise the 4:2 S/PDIF Input Multiplexer. The select line control is accessed using the RXPSEL[1:0] pins. Unused multiplexer inputs should be left floating or tied to AGND. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for recommended input circuits. |  |  |  |

| Pin Name         | Pin #   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RXN              | 2       | <b>Negative AES3/SPDIF Input</b> ( <i>Input</i> ) - Single-ended or differential receiver input carrying AES3 or S/PDIF encoded digital data. Used along with RXP[3:0] to form an AES3 differential input. In single-ended operation this should be AC coupled to ground through a capacitor. See "External AES3/SPDIF/IEC60958 Receiver Components" on page 50 for recommended input circuits. |  |

| ОМСК             | 22      | <b>System Clock</b> ( <i>Input</i> ) - OMCK System Clock Mode is enabled by a transition (rising edge active) on OMCK after reset. When enabled, the clock signal input on this pin is automatically output through RMCK on PLL unlock. See "OMCK System Clock Mode" on page 28.                                                                                                                |  |

| RMCK             | 21      | <b>Input Section Recovered Master Clock</b> ( <i>Output</i> ) - Input section recovered master clock output from the PLL. Frequency is 256x the sample rate ( $F_s$ ) when the U pin is pulled down by a 47 k $\Omega$ resistor to DGND. Frequency is 128x the sample rate ( $F_s$ ) when the U pin is pulled up by a 47 k $\Omega$ resistor to VL.                                             |  |

| OSCLK            | 24      | Serial Audio Output Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin                                                                                                                                                                                                                                                                                                 |  |

| OLRCK            | 25      | Serial Audio Output Left/Right Clock ( <i>Input/Output</i> ) - Word rate clock for the audio data on the SDOUT pin. Frequency will be the output sample rate (Fs)                                                                                                                                                                                                                               |  |

| SDOUT            | 23      | <b>Serial Audio Output Data</b> ( <i>Output</i> ) - Audio data serial output pin. This pin must be pulled low to DGND through a 47 k $\Omega$ resistor to place the part in Hardware Mode.                                                                                                                                                                                                      |  |